Transmisi Synchronous dan Asynchronous

Hello semua, kembali lagi dengan kami sang Blogger pemula. Pada kesempatan kemarin kami telah membagikan mengenai Komunikasi Data. Kali ini kami akan membagikan materi mengenai Transmisi Synchronous dan Asynchronous. Jadi mari kita langsung saja menuju pembahasan.

Transmisi Synchronous dan Asynchronous

Transmisi data seri; yakni di mana. Data yang ditransfer lebih dari satu sinyal dibandingkan dengan sinyal pada saluran paralel, sebagaimana yang biasa dilakukan dengan perangkat 1/0 dan jalur sinyal komputer internal. Dengan transmisi seri, elemen-elemen pensinyalan dikirim sepanjang jalur sekaligus. Setiap elemen-elemen pensinyalan bisa berarti:

- Kurang dari satu bit: Dalam hal ini, contohnya, dengan pengkodean Manchester.

- Satu bit: Contohnya, NRZ-L digital dan FSK analog.

- Lebih dari satu bit: Contohnya, QPSK.

Untuk

menyederhanakan pembahasan selanjutnya, kita mengasumsikan satu bit per elemen

pensinyalan kecuali bila yang sebaliknya yang dinyatakan. Pembahasan ini tidak

secara langsung dipengaruhi oleh simplifikasi

ini.

|

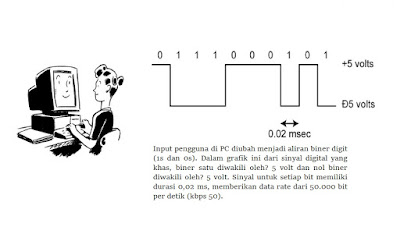

| gambar penerima data digital melibatkan pemeriksaan sinyal |

Perhatikan gambar di

atas dimana penerima data digital melibatkan pemeriksaan sinyal yang datang

satu kali per bit waktu untuk menentukan nilai biner-nya. Salah satu kesulitan

dalam menjalankan proses semacam itu adalah karena berbagai gangguan transmisi

akan merusak sinyal sehingga kadang-kadang terjadi kesalahan. Problem ini

terjadi dikarenakan adanya kesulitan dalam hal waktu. Pada dasarnya tidak ada

masalah bagi receiver untuk memeriksa bit-bit yang datang sebagaimana mestinya,

yang harus diketahui adalah waktu kedatangan serta durasi dari setiap bit pada

saat diterima.

Seandainya, pengirim

mentransmisikan suatu deretan bit-bit data. Pengirim memiliki sebuah detak yang

menentukan waktu bit-bit yang ditransmisikan. Sebagai contoh, bila data

ditransmisikan pada satu juta bit per detik (1 Mbps), maka satu bit akan

ditransmisikan setiap 1 / 106 = 1 mikrodetik (µs), seperti yang

tercatat pada detak pengirim. Biasanya, receiver akan berupaya memeriksa media

di tengah-tengah waktu penerimaan bit. Receiver akan menghitung waktu

sampel-sampel tersebut pada interval satu bit. Pada contoh tersebut,

pemeriksaan akan terjadi setiap 1 µs. Bila

receiver menghitung waktu sampel-sampel berdasarkan atas detak miliknya

sendiri, akan muncul masalah bila detak pada transmitter dan receiver tidak

sama. Bila terdapat geseran sebesar 1 persen (detak pada receiver satu persen

lebih cepat atau lebih lambat dibanding detak pada transmitter), maka pemeriksaan

pertama menjadi 0,01 bit waktu (0,01 µs) jauhnya

dari pusat bit (pusat bit adalah 5 mulai dari bit awal sampai bit terakhir).

Setelah 50 sampel atau lebih, receiver kemungkinan mengalami kesalahan yang

disebabkan karena pemeriksaan dilakukan pada waktu yang salah (50 x 0,1 = 5 µs). Bila perbedaan waktunya lebih kecil,

akan tetap terjadi kesalahan, namun

receiver akan mengambil tindakan lebih dulu dibanding transmitter, terlebih

bila transmitter mengirimkan deretan bit yang cukup panjang dan bila memang tidak

ada langkah-langkah yang diambil untuk mensinkronkan transmitter dan receiver.

Transmisi

Asychronous

Ada dua pendekatan

yang paling umum untuk mencapai sinkronisasi yang diharapkan. Pertama disebut

transmisi asynchronous. Strategi dalam skema ini adalah menghindari problem

yang berkaitan dengan waktu dengan cara tidak mengirimkan deretan bit yang

panjang dan tidak putus-putus. Jadi, data ditransmisikan satu karakter

sekaligus, dimana setiap karakter panjangnya lima sampai delapan bit. Waktu

atau sinkronisasi harus dipertahankan hanya didalam setiap karakter; receiver

memiliki peluang melakukan sinkronisasi pada permulaan setiap karakter baru.

|

Gambar Transmisi

Asynchronous

|

Gambar di atas

memberi penjelasan mengenai teknik ini. Bila tidak ada karakter yang

ditransmisikan, jalur diantara transmitter dan receiver dinyatakan dalam status

idle. Definisi idle ekuivalen terhadap elemen-elemen pensinyalan untuk biner 1.

Sehingga, idle bisa berupa adanya tegangan negatif pada jalur tersebut.

Permulaan karakter ditandai dengan suatu start

bit dengan nilai biner 0. Ini diikuti dengan lima sampai delapan bit yang

sebenarnya merupakan karakter. Bit-bit karakter ditansmisikan yang dimulai

dengan bit yang secara signifikan merupakan yang paling sedikit. Sebagai

contoh, untuk karakter IRA, bit pertama yang ditransmisikan adalah bit yang

diberi label bl dalam Tabel 3.1.

Biasanya, bit-bit data diikuti oleh sebuah bit parittas, yang karenanya berada

dalam posisi bit yang paling signifikan. Bit paritas disusun oleh transmitter

semacam itu. Jumlah total bit-bit dalam karakter, termasuk bit paritas, bisa

genap (paritas genap) atau ganjil (paritas ganjil), tergantung ketentuan yang digunakan. Bit ini

dipergunakan oleh receiver untuk mendeteksi keselahan, sebagaimana yang dibahas

di Bab 7. Yang dimaksud dengan elemen akhir adalah stop element, yang berupa biner 1. Panjang minimum untuk elemen

akhir ditentukan, biasanya 1, 1, 5 atau 2 kali durasi bit biasa. Tidak adanya nilai

maksimum juga ditentukan. Karena elemen akhir sama dengan status idle,

transmitter tidak akan terus mentransmisikan elemen akhir sampai elemen akhir

siap mengirimkan karakter berikutnya.

Bila deretan

karakter dikirim, interval diantara kedua karakter tersebut menjadi seragam dan

setara terhadap elemen akhir. Sebagai

contoh, bila elemen akhir sebesar satu bit waktu dan karakter IRA ABC dikirim

(dengan bit paritas genap), polanya adalah 01000001010010000101011000011111

... 111. Bit awal (0) memulai

deretan waktu untuk sembilan elemen berikutnya, yang berupa 7-bit kode IRA, bit

paritas, dan elemen akhir. Pada status idle, receiver mencari

transisi dari 1 sampai 0 untuk menandai permulaan karakter berikutnya dan kemudian

memeriksa sinyal-sinyal input pada satu bit interval untuk tujuh interval.

Dilanjutkan dengan mencari transisi 1 sampai 0 berikutnya, yang akan muncul

tidak lebih cepat dibanding satu bit waktu lagi.

Transmisi

asynchronous sangat sederhana dan murah namun memerlukan tambahan dua sampai

tiga bit per karakter. Sebagai contoh, untuk karakter 8-bit tanpa bit

prioritas, menggunakan elemen akhir sepanjang I-bit, dua dari setiap sepuluh

bit tidak membawa informasi, namun mereka hanya untuk sinkronisasi saja;

sehingga tambahannya adalah 20 persen. Tentu saja, tambahan persentase dapat

dikurangi dengan mengirimkan blok bit yang lebih besar diantara bit awal dan

elemen akhir. Bagaimanapun juga, seperti yang ditunjukkan dalam gambar 6.1c,

semakin besar blok bit, maka semakin besar tumpukan kesalahan. Untuk mencapai

tingkat efisiensi yang lebih besar, digunakan transmisi synchronous, yang

merupakan bentuk lain dari sinkronisasi.

Transmisi

Synchronous

Dengan transmisi synchronous, suatu blok bit

ditransmisikan dalam suatu deretan yang cukup mantap tanpa kode start dan stop.

Panjang blok tersebut bisa terdiri dari bit-bit yang begitu banyak. Untuk

mencegah ketidaksesuaian waktu di antara transmitter dan receiver, detak-nya

dengan cara apapun harus dibuat sinkron. Salah satu kemungkinannya adalah

dengan menyediakan sebuah jalur detak terpisah diantara transmitter dan

receiver. Salah satu sisi (transmitter maupun receiver) mengatur jalur secara

teratur dengan satu pulsa pendek per bit waktu. Sisi yang lain mengunakan pulsa

reguler ini sebagai detak. Teknik ini akan bekerja dengan baik untuk jarak

pendek, namun untuk jarak yang lumayan panjang pulsa detak akan menjadi sasaran

gangguan-gangguan yang sama seperti yang terjadi pada sinyal data, ditambah

lagi dengan adanya kesalahan dalam hal waktu. Alternatif lain, dengan menyimpan

informasi pewaktuan pada sinyal data. Untuk sinyal-sinyal digital, hal ini bisa

diperoleh dengan pengkodean Manchester atau Manchester Diferensial. Sedangkan

untuk sinyal-sinyal analog, terdapat sejumlah teknik yang dapat dipergunakan;

misalnya, frekuensi pembawa itu sendiri juga dapat dipergunakan untuk

mensinkronkan receiver didasarkan atas fase fekuensi pembawa.

Dengan transmisi

synchronous, terdapat level sinkronisasi lain yang diperlukan, yang

memungkinkan bagi receiver menentukan awal dan akhir suatu blok data. Untuk

mencapai hal ini, setiap blok diawali dengan pola bit preamble dan biasanya diakhiri dengan pola bit postamble. Selain itu, bit-bit yang lain ditambahkan ke blok data

yang membawa informasi kontrol yang dipergunakan dalam prosedur kontrol data

link sebagaimana yang didiskusikan di Bab 7. Data plus preamble, postamble, dan

informasi kontrol disebut frame.

Bentuk frame yang tepat tergantung pada prosedur kontrol data link apa yang berlaku.

|

Gambar Format Frame

Synchronous

|

Gambar di atas

menunjukkan, menurut istilah umum, bentuk frame khusus untuk transmisi

synchronous. Biasanya, frame diawali dengan suatu preamble yang disebut flag,

yang panjangnya delapan bit. Flag yang sama dipergunakan sebagai postamble.

Receiver mencari pola flag untuk menandai permulaan frame. Ini diikuti dengan

beberapa bit-bit kontrol, kemudian bit-bit data (panjangnya variabel untuk

sebagian besar protokol), bit-bit kontrol lagi, dan terakhir flag diulang lagi.

Untuk blok data yang

cukup besar, transmisi synchronous jauh lebih efisien dibanding transmisi

asynchronous. Transmisi asynchronous memerlukan tambahan 20 persen atau bahkan

lebih Informasi kontrol, preamble, dan postamble dalam transmisi synchronous

biasanya kurang dari 100 bit. Sebagai contoh, salah satu dari skema yang paling

umum, HDLC (digambarkan di Bab 7), memuat 48 bit kontrol, preamble, dan

postamble. Sehingga, untuk 1000 karakter blok data, masing-masing frame

berisikan 48 bit tambahan dan 1000 x 8 = 8.000 bit data, sedangkan persentase

kelebihannya hanya 48/8048 x 100% = 0,6%.

Demikian yang dapat kami bagikan, terima kasih telah berkunjung dan semoga bermanfaat.

Komentar

Posting Komentar